本帖最后由 haierccc 于 2021-5-10 20:25 编辑

发展高性能存储器件在现代电子学的革新中扮演着关键角色。

在海量数据存储和超快数据处理的需求驱动下,发展超快非易失性存储器件势在必行。当前在存储领域里面临的主要瓶颈问题有:操作速度慢、数据保持时间短、数据维持性差、擦除/写入比低等。特别是,随着器件尺寸的进一步缩微化,为了满足日益增长的存储容量的需求,硅基技术很快就会达到极限。其中的一个关键挑战在于超薄硅体材表面不可避免的存在大量的界面悬挂键,从而造成器件性能的严重退化。因此亟需寻找原子级锐利的界面,并且能将其无缝地集成到器件层级结构中。

在所有的候选研究体系中,二维原子晶体及其异质结构这个近年来涌现出来的新型材料体系具有理想的原子级平坦的表面,没有表面悬挂键。而且它们对短沟道效应免疫,从而使得高效的静电调控和力学柔性成为了可能。之前,研究者曾经利用二维原子晶体来构筑闪存器件,然而器件性能并不理想。这些闪存器件的编程时间非常长,在数百微秒到数秒量级;擦除/写入比也很低,在10到106的范围。虽然,利用半浮栅的器件结构成功将编程时间缩短至数十纳秒,但是数据保持时间非常短,只有数秒,使得其并不适用于长期存储。理论模拟也表明,基于层状材料的平面结构制作的理想浮栅存储器件,其操作时间可以快至纳秒量级。然而,超快浮栅存储器件至今没有被研制成功。

针对这一重大挑战,中国科学院物理研究所/北京凝聚态物理国家研究中心高鸿钧院士研究团队的博士生吴良妹和鲍丽宏副研究员等利用二维范德瓦尔斯异质结的原子级锐利界面及增强的界面耦合特性,无需修改商用的器件结构,首次成功构筑了超快、非易失浮栅存储器件,成功实现了其纳秒级(~20 ns)的读写时间(商用闪存器件为百微秒),极高的擦除/写入比(~1010)和极长的存储时间(10年以上)。

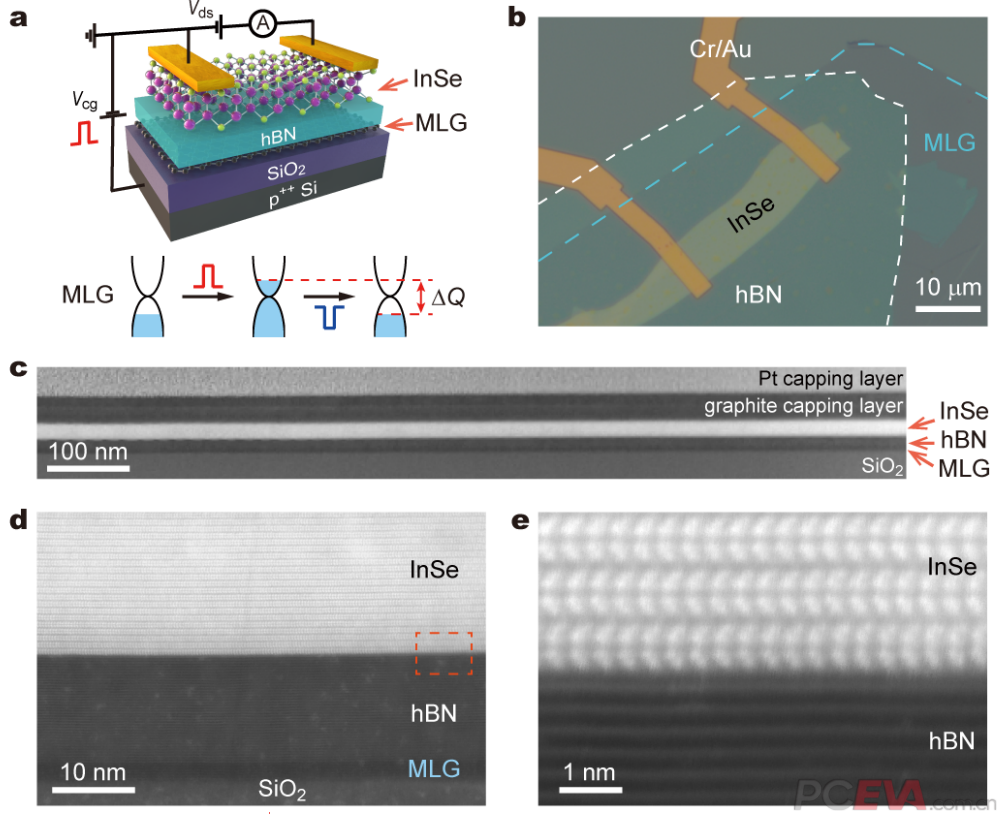

图1. 基于InSe/hBN/MLG范德瓦尔斯异质结的浮栅场效应晶体管的器件结构及原子级锐利的界面特性。

图1a和1b是器件的结构示意图及光学显微照片,其中InSe是沟道、hBN是隧穿势垒层、MLG是浮栅、SiO2是控制栅介电层、重掺硅是控制栅。高分辨扫描透射电子显微镜表征显示InSe/hBN/MLG异质结具有原子级锐利的界面特性(图1 c-e)。基本的存储特性表征显示浮栅场效应晶体管具有大的存储窗口(图2)。通过在控制栅上施加一个幅值为+17.7/-17.7 V、半峰宽为160 ns的脉冲电压对浮栅存储器进行编程/擦除操作,浮栅存储器表现出极高的擦除/写入比(擦除态/编程态电流比为~1010)、极长的存储时间(大于10年)和优异的耐久性(可重读擦写次数大于2000)(图3)。进一步利用自主搭建的超短脉冲电源(半峰宽为21 ns,幅值为+20.2/-20.8 V)来对器件进行写入/擦除操作,仍然能成功实现高的擦除/写入比(1010),及超快读取(图4 a-d);此外,将InSe沟道替换成MoS2,同样能实现超快的编程/擦除操作,表明了具有原子级锐利界面的范德瓦尔斯异质结构实现超快浮栅存储器的普适性。更进一步受益于极高的擦除/写入比,他们通过优化hBN的厚度,实现了浮栅存储器的多值存储(图4 e)。

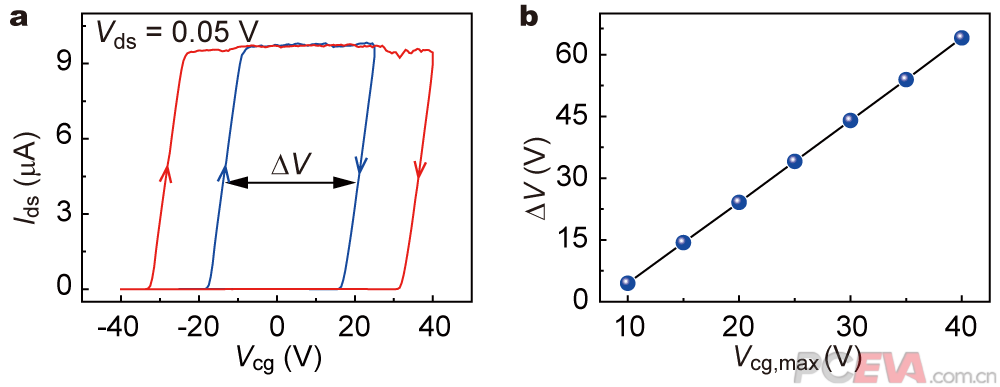

图2. 基于范德瓦尔斯异质结的浮栅场效应晶体管的基本存储特性表征显示其具有大存储窗口。

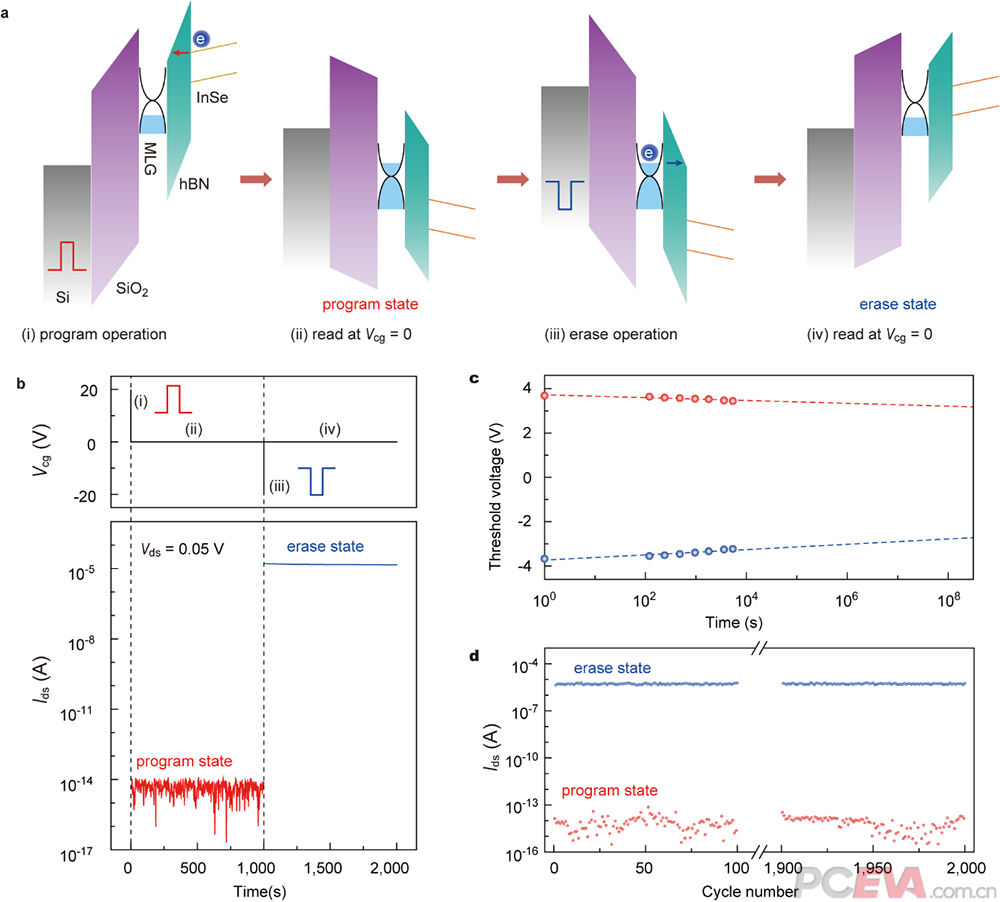

图3. 基于范德瓦尔斯异质结的浮栅存储器的擦除/写入操作,超高擦除/写入比,数据存储的非易失性及耐久性。

a. 基于范德瓦尔斯异质结的浮栅存储器的编程、擦除及相应的读取操作原理。b. 在控制栅上施加幅值为+17.7/-17.7 V、半峰宽为160 ns的脉冲电压成功实现浮栅存储器的编程/擦除操作,擦除/写入比高达~1010。c. 对浮栅存储器进行编程/擦除操作后,编程态和擦除态的阈值电压随时间的变化关系表明浮栅存储器具有非易失的数据保持能力(十年以上)。d. 对浮栅存储器反复进行2000次以上的擦除/写入操作,其擦除态和编程态电流几乎没有任何变化,表明浮栅存储器的优异耐久性能。

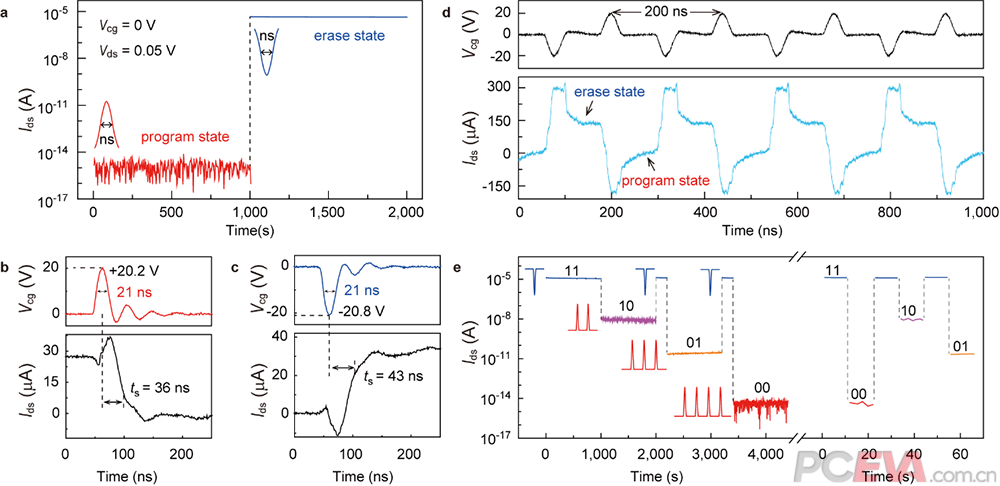

图4. 基于范德瓦尔斯异质结的浮栅存储器的超快写入/擦除操作及其多值存储特性。

a. 在控制栅上施加幅值为+20.2/-20.8 V、半峰宽为21 ns的脉冲电压成功实现浮栅存储器的编程/擦除操作,擦除/写入比高达~1010。b-c. 浮栅存储器在经过编程(b)和擦除(c)脉冲后的超快响应。d. 对浮栅存储器进行间隔为~100 ns的连续擦除、编程操作后的电流特性。e. 浮栅存储器的多值(2-bit)存储特性。

基于原子级锐利界面的范德瓦尔斯异质结超快浮栅存储器具有和动态随机存取存储器(10 ns)相当的编程速度,同时具备非易失、大容量的存储特性。对于发展未来高性能非易失存储器具有重要意义,也为进一步开发基于范德瓦尔斯异质结构的高性能电子器件提供了一种创新思路。未来在应用上的挑战主要是高质量、大面积hBN和二维原子晶体沟道材料的外延生长及其集成器件的构筑。

相关结果以“Atomicallysharp interface enabled ultrahigh-speed, nonvolatile memory device”为题在5月3日的Nature Nanotechnology(2021)在线发表。吴良妹(已毕业)、王爱伟(已毕业)、时金安(中国科学院大学)和严佳浩(已毕业)为共同第一作者,鲍丽宏副研究员、欧阳敏教授和高鸿钧院士为共同联系作者。中国科学院大学周武教授等参与了该项研究。该工作得到了基金委(61888102)、科技部(2016YFA0202300、2018YFA0305800)以及中国科学院(XDB30000000、XDB28000000、Y201902)的资助。

--------------------------------------------------

吾之中华

吾之强大的中华

吾之积弱的中华

吾之美丽的中华

吾之丑陋的中华

吾之多灾多难的中华

吾之强敌环伺的中华

今日终于看到曙光

|